射頻SOI開關RF SOI Switch雖然是由電晶體(transistor)構成,但在工作上比較類似一個被動元件例如衰減器,假設有一個開關插損(insertion loss IL)為0.5dB,那在接收鏈路計算上經過此開關SNR會惡化0.5dB (訊號變小)整體的靈敏度會跟著降低0.5dB,但有時候測起來下降幅度會超過預期! 而且還有頻率選擇的行為,怎麼經過一個開關會有這種現象呢?

開關的狀態與控制電壓

早期手機射頻開關都是以GaAs pHEMT為主,現在還有部分的WiFi產品都還是再用pHEMT制程來設計開關,兩個材料有什麼區別這裡就不探討有興趣的可以參考[1]或網路上搜一下也有很多相關的文章,但在查之前我們用商業邏輯角度思考一下答案,SOI相較之下一定是提供非常好的性價比,所以即使特性上有差那麼一點還是佔據了大部分的市場份額,但還有少部分須要pHEMT開關的性能優勢,但優勢不夠多所以漸漸被SOI取代。

|

| [1] SKYWORKS APPNOTE |

剛工作的時候那時候手機還是GSM 四頻機Quad-Band為頂規的年代,我不確定是誰把SOI導入到主流手機功率放大器模組開內部關上,但我接觸的第一個商用SOI產品是Renesas 88163 (很多人不知道Renesas 早期有賣功率放大器模組吧),當時的確也是讓大家Wow了一聲。

開關SW的開關邏輯在開啟的狀態ON state希望VGD(Voltage between Gate and Drain)越大越好,但不能高過元件的工作電壓,例如一般常見的2.5V器件 VGD標準為2.5V,反之關的狀態OFF

state VGD要負越大越好,但電壓差也不能超過2.5V,雖然有些時候會偷一點點電壓讓性能夠好一些[2],但範圍也不能太大否則會影響器件的長期使用的可靠性(Reliability),早期pHEMT與SOI開關的控制方式為單電壓邏輯控制(Single

Positive Supply),所以電晶體要開VG給2.5V然後VD與VS接到0V這樣VGD為2.5V,如果要電晶體關閉因為只有一組電壓,此時VG給0V但VD與VS 給2.5V,這樣VGD就等於-2.5V如下圖所示:

這裡以單刀雙擲SPDT(single pole double throw)開關來解釋單電源控制的實際配置,每個開關單元不能直接接在一起,須要在每個開關單元之間放置隔直電容(DC

blocking capacitor)來避免控制電位短路干擾,假設當RF1這一路要通的時候,另外RF2通路要關閉,每個開關單位的狀態如下,電晶體除了閘極Gate要給定控制電壓外,也要同時提供源極Source與汲極

Drain電壓狀態,所以須要隔直電容來避免直流短路。

但這種控制方法好處是只須要一個正電壓源,邏輯簡單切換速度快,並且沒有其他額外的雜散產生(這個等一下會提到),但缺點也很明顯須要很多晶片等級的電容,在開關埠數增加電容面積會變的很可觀,晶片面積就是成本,所以目前主流採用的控制方法都是正負電壓源控制方法,如下圖改成負電壓控制整個電路的隔直電容都可以移除,因為RF口電壓為0V,所以大部分情形也不須要外部PCB的隔直電容,但注意不能有其他DC電壓由外部灌入影響開關器件的控制狀態。

負電壓產生器Negative

Charge Pump

那問題來了負電壓哪裡來?一般生活中如果有兩個電池,把正負極相連的節點當作系統參考地,這樣原本的負極與正極就會有是一對正負電壓源,但一般的手機電池就是一正一負輸出,沒有負電壓這個配置。

實際上是須要一個負電壓產生器Negative Charge Pump Circuit,網上搜尋Negative

Charge Pump電路設計有很多類型,但基本原理是差不多的,Pump泵浦這個字很具向化,舉例來說類似拿著水瓢在水龍頭接了水然後走到大水桶注水,只是電路上這臉盤與水桶都是電容器,下圖為工作原理流程,逐步來看一下:

Step 1: 將電容Cp(水瓢)去取電,電容會被充電到電源電壓+5V

Step 2: 取下電容, 此時電容如同一個+5V小電池

Step 3: 把電容反轉一下,極性從+5V變成-5V (這個只是參考點變更)

Step 4: 接上負載電容CL回路

Step 5: 接上回路電容Cp往負載電容CL充電,電壓VL由0V充電到-2.5V.

然後重複以上的動作負載電容電壓會逐步的充電到-5V,這條件下需要4次才能把電壓充到90%的目標電壓,當然這個條件是基於充電電容Cp與負載電容CL是一樣大,而且負載沒有在抽電的情況下。

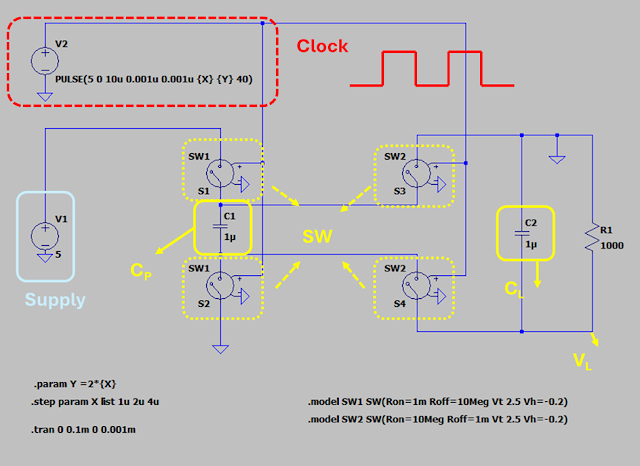

實際電路實現參考[3]用LTspice搭建一個理想的負電壓產生器,電路上除了充電電容Cp與負載電容CL外,還有幾個理想開關來決定充電電容Cp是在跟電源取電與跟負載電容CL放電,這切換動作由時鐘Clock來決定。

直觀上時鐘速度越快(clock rate)或Cp電容越大充電速度也越快,這個速度就會影響電路的啟動時間(settling

time),但設定太快干擾的問題會惡化,所以目前常見的作法會在前面一段時間時鐘的速度較快當穩定後,在切換成較低速率的時鐘來維持負電壓輸出降低干擾的問題。

時鐘引起的雜散干擾Spurious Emission caused by clock

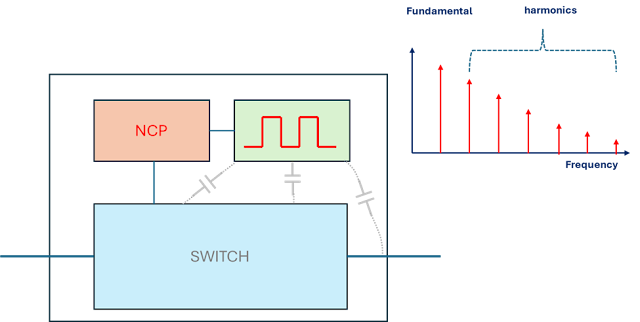

上面講了這麼多主要是要帶出SOI射頻開關,內部負電壓產生器須要時鐘訊號,既然有時鐘訊號在頻譜上就會產生對應的諧波造成干擾,常解desense的朋友一定知道,有人的地方就有江湖、有時鐘的地方就有干擾,當然全部的數位訊號(方波)都是,只是一般不會想到開關自己內部也有時鐘,找錯方向一直在找周邊的干擾源。

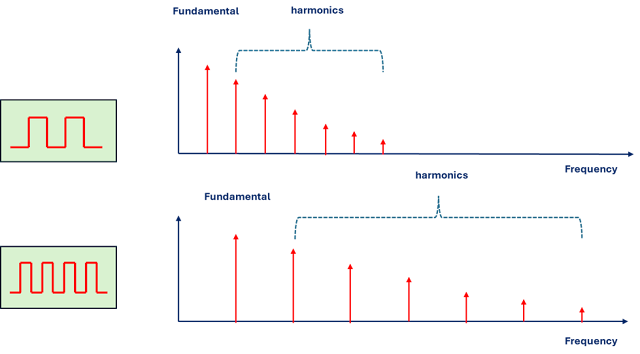

剛剛提到為什麼負電壓內部時鐘頻率越高干擾就越大?如下圖比較兩個方波訊號原本的頻率為f0第二個訊號頻率為2*f0,振福大小相同,把這兩個訊號轉換成頻譜訊號比較主頻fundamental與諧波harmonics訊號大小一樣,但2*f0時鐘訊號整體頻譜平移到高頻,雖然每個開關干擾成因都不太一樣,但設計目標都是希望時鐘訊號是跟其他電路隔離,可以無論考慮在周詳時鐘電路就在開關主體旁邊,兩個電路模組會有”寄生耦合”產生,而電容的阻抗公式為Zc=1/wC所以頻率越高電容的阻抗Zc就越小,時鐘訊號也就更容易順著寄生電路耦合到其他電路上造成干擾。

開關規格書指標

那反應在開關規格書上面應該看哪個指標? 參考[4] Peregrine部分產品的規格書會提到Spurious

Performance這指標,其中也提到如果雜散要更低一些,那就外給負電壓,當外部偵測到負電壓內部應該會把NCP關閉就變成一個傳統的開關。

但大部分應用在手機主流SOI開關規格書都不會寫這指標,包含國際大廠與國內廠商,那不寫是代表內部沒有負電壓產生器是用單電源控制方法嗎?

其實大部分都還是用負電壓控制方法,沒有寫這規格很多時候可能是客戶沒問沒要求,不知不覺變成一個慣例,但頭部產商都會有自己內部對應的驗證方法與規格來保證其產品特性。

測試驗證方法

測試驗證開關雜散的方法就很直觀了,但有一些細節這裡可能會遺漏,如下圖在驗證開關雜散直接接頻譜測就可以,但是這雜散功率很小,而且內部時鐘沒有鎖相回路並不是那麼穩定,所以在測試的時候須要在開關與頻譜之間接個低雜訊放大器,降低整體量測環境的底噪,頻譜的RBW頻寬不要為了”肉眼”看到底噪很低設定的很小,這除了速度慢外也很容易錯過雜散訊號,因為雜散的訊號頻率不是那麼穩定,所以建議可以設定在100kHz左右。

上面為小訊號測試方法,量測雜訊高次諧波直接洩漏到射頻口的大小,另外一個為大訊號測試,開關在大功率的時候非線性特性會讓開關如同一個混頻器,時鐘雜散功率較低頻的訊號會與射頻訊號混頻帶到射頻接收頻段(FDD

band),驗證的方法跟小訊號量測方法類似,但須要對應的雙工器與射頻放大器,還有大訊號驗證與小訊號驗證是兩個獨立的測項。

最後最直接的方式就是直接上手機驗證,直接看手機應用上結果是不是符合需求,如果是一個pin

to pin疊代的產品這個作法的確比較有效率,但可能會有疑慮要看多少台手機才算OK? 只看這一台能代表全部嗎? 是不是要多驗證幾台? 而且如果是新產品可能會找不到對應的樣機驗證。

雖然使用負電壓控制有時鐘干擾問題、開啟穩定時間的問題,但並不是不能克服,良好的設計下也都能滿足目前通訊系統4G/5G與WiFi的應用,目前主流SOI開關還是以負電壓控制為主。單電源控制放按須要隔直電容造成晶片面積增加,但還是有其優點所以也有人提出新的單電源架構來改善這些缺點,例如文章[5]就提中一個新的單電源架構,整篇內容還不錯喜歡進一步研究的朋友可以下載來看看。

參考文獻

[1] SKYWORKS APPLICTION, “Choosing RF Switches For Smart

Mobile Device Applications”

[2] F. Gianesello, A. Monroy, V. Vialla1, E.

Canderle, G. Bertrand1, M. Buczko1, M. Coly,Jeff Nowakowski1, N. Revil, L.

Rolland, D. Gloria, A. Juge1, S. Gachon, J.P. Aubert and E. Granger, “Highly

linear and sub 120 fs Ron x Coff 130 nm RF SOI Technology Targeting 5G Carrier

Aggregation RF Switches and FEM SOC”, SiRF 2016

[3] Exploring Output Ripple in a Negative Voltage

Charge Pump Using LTspice

https://www.allaboutcircuits.com/technical-articles/exploring-a-negative-voltage-charge-pump-in-ltspice-output-ripple/

[4] Peregrine semiconductor, “PE42520 Datasheet”

[5] Donggu Im, Member, IEEE, Bum-Kyum Kim, Do-Kyung

Im, and Kwyro Lee, Fellow, IEEE. "A Stacked-FET Linear SOI CMOS Cellular

Antenna Switch With an Extremely Low-Power Biasing Strategy", IEEE

TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL. 63, NO. 6, JUNE 2015