前言

ESD......產品上市前的最後一哩路,讓無數工程師大聲吶喊WTF的問題,電子業從IC到產品,一定都會接觸到ESD的個問題,終端產品成品會用ESD槍( IEC 61000-4-2)來模擬環境的靜電傷害,IC元件等級會用HBM(JEDEC/MIL)來模擬生產過程的靜電等級,或測試插座突破Surge/對岸的朋友叫做浪湧 IEC 61000-4-5的標準,在測試訊號上原理基本都是相同,先針對機器內部電容充電到指定電壓後,然後再對待測物放電(Discharge),就如同電池有正負電極一樣,HBM, ESD Gun或Surge等都是紅黑訊號接到待測物的兩端點進行放電。以下是HBM與ESD Gun的簡易模型但這兩個標準最大的差異在於放電路徑上面的電阻大小,但這也沒有誰對誰錯,畢竟誰知道人體等校電阻到底哪個比較正確,

所以標準在於讓全部元件製造商都有一個共同評比環境下進行而已

,這裡我們假設兩個模型內部電容都分別充電到1000V,待測物DUT會在瞬間呈現短路狀況,此時流過DUT的瞬間電流最大分別為:

> HBM: 1000V/1500R=0.66A

> ESD Gun: 1000V/330R =3.03A

可以可以看出來一樣是1000V的測試,不同的標準下最大電流會相差5倍,實際電路以我工作經驗也大概會差3倍以上,但這倍率並非絕對,每個電路狀況可能不太一樣,就跟冬天時候有人容易被靜電電到,有人就不容易被電到感覺很類似。

|

| HBM vs IEC 61000-4-2 |

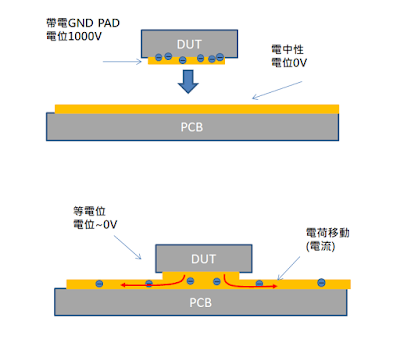

CDM Charge Device Mode行為模式

CDM Charge Device Mode就沒辦法像上面的測試一樣,可以拉出兩根紅黑線接上兩個IO pin這麼單純,CDM主要精神是在模擬元件在還組裝過程,因為環境沒有控制好累積靜電在原件身上,本身帶電不會怎樣,但對人放電問題就大了。在與主機板PCB碰觸的瞬間造成的放電現象,如果你冬天常被靜電電到就更容易理解,身上因為種種遠因累積了大量電荷,這些電荷平常摸木頭等絕緣表面的時候會留在原處不動,但有機會接觸導體比方說喇叭鎖門把,鐵櫃甚至拉鍊等就會迅速移動也就是大電流產生,雖然瞬間電流很大但時間很短,所以總能量並不大,就是痛一下下,不然不就冬天一到不就一堆人被靜電電成黑炭........

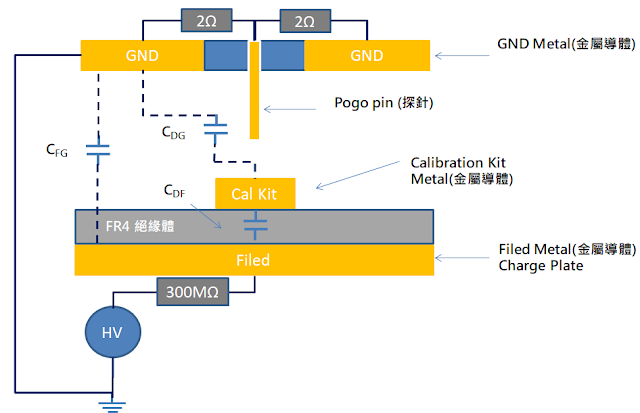

CDM校正電路模型

所有標準都一樣必須要能夠可執行與複製(executable and reproducible),所以JEDEC/AEC就規範了標準測試方法來模擬CDM的行為模式,會了要模擬CDM的行為,我們先講一下測試環境,一塊很大的金屬充電板Charge Plate與待測物隔著一個FR4絕緣材質(當然規範中有定義其厚度),校正模塊為一塊圓形金屬塊,但放置在FR4上面與Charge Plate之間電容量CDG為4pF. (這一點就JEDEC and AEC就都規範不同的校正電容,但骨子裡是一樣的原理)。 |

| CDM放電模型 |

Field Charge and Filed Induced 充電行為, 初始條件Initial Condition

CDM是在模擬元件在生產過產累積的電荷沒有正常被釋放掉導致的放電行為,我們先拿Cal Kit當作待測物,放置在Filed Plate上面後,然後開啟HV高壓電源供應器,上面的探針還沒點到校正金屬圓盤(CalKit Metal)。整個電路會有三個基本電容CDF, CDG與CFG,。CDF不用說就是DUT與Filed之間的等校電容量,在這裡我們以[3]AEC 4pF為例,CDG則是與上面GND Plate等校出來的電容量,但這個通常要遠小於CDG,另外一個是CFG則是上方的GND Metal與下面的Filed Metal等校的電容值,這個值就取決Pogo pin的長度與GND Plate的面積(平板電容公式),這裡我沒有找到一個明確的數值,但有一篇blog[1]]有提到EM模擬約16pF,我們姑且先用16pF來觀察。

下面以250V為例子,VDUT最後穩定的電壓與CDF and CDG相關,但因為CDG都很小,最以一般來說DUT都會很接近250V。

|

| 初始條件Initial Condition |

Pogo Pin等校電路與放電waveform

下圖AEC_Q100-011C1文件[3]中有規範校正電路的放電電流波形(Current Waveform),可以看出來電流有Dampping的現象,這也代表整個放電路徑中要有電感Inductor存在,否怎一個RC充放電網路是不會有Damping(上下擺動)的行為。 |

| AEC_Q100-011C1 |

我們以 IEC 61000-4-2,google IEC 61000-4-2 Spice Model就可以找到好幾種合成模型,至於硬體部分ESD槍內部結構怎麼製作,下圖就是其中一個。[2][5]

|

| IEC 61000-4-2 Spice Model |

不好捉摸的Field Charge行為

從CDM校正板的放電模型可以理解整個Device充放電的機制,所以也沒有一台CDM generators能夠伸出一正一負的紅黑線來執行驗證,整個驗證需要一台高壓電源供應器與對應的充電板Field Charge Plate與Pogo Pin與對應的置具平台。另外直觀上可以知道CDM的放電Peak會遠高於HBM or ESD Gun,但時間短很多<1ns,但瞬間即是永恆,傷害一旦而且實際電路放電行在Spice Model上面的描述就變得更為複雜,放電路徑可能變得很多元,不良樣品分析與改善對策也相對於HBM/Surge/ESD Gun來的複雜。

參考文獻

[1] Simulating Small Device CDM Using Spice

https://incompliancemag.com/article/simulating-small-device-cdm-using-spice/

[2] A SIMPLE SPICE ESD GENERATOR CIRCUIT BASED ON IEC61000-4-2 STANDARD

https://www.youspice.com/simple-spice-esd-generator-circuit-based-on-iec61000-4-2-standard/

[3] AEC, AEC - Q100-011 Rev-C1, CHARGED DEVICE MODEL (CDM), ELECTROSTATIC DISCHARGE TEST

http://www.aecouncil.com/Documents/AEC_Q100-011C1.pdf

[4] IEEE, Predict the Product Specific CDM Stress Using Measurement-based Models of CDM Discharge Heads

[5] Qorvo, SEED Methodology for Optimizing an ESD RF Front-End Design

https://www.qorvo.com/design-hub/blog/seed-methodology-for-optimizing-an-esd-rf-front-end-design

[6] IEEE,Progress Towards a Joint ESDA/JEDEC CDM Standard:Methods, Experiments, and Results

沒有留言:

張貼留言