三用電錶但其實早就不只有三種用途(電阻,電壓,電流),應該說說萬用儀錶,但講萬用儀錶這樣有點low low的,上班要講Multi-meter聽起來比較International,也是實驗室是最常被其他部門幹走的儀器之一,最近上網Survey想說買一台自己用,之前實驗室常購買的牌子像是Keithley (被Tektronix併購)或買綜合測試儀凹廠商送的Keysight DMM,規格上比較常見的是 6 1/2 Digits 6.5位元,那時候要買高階一點就買7.5位元或8.5位元。

|

| https://www.keysight.com/zh-TW/pcx-2832403/digital-multimeters-dmm?nid=-32052.0.00&cc=TW&lc=cht |

解析度 Resolution

自己花錢買不可能動不動買台上數十萬的Keysight或Tektronix專業的儀表,上購物網站看價格大概從數百塊到數千都有,功能上有所差異但比較讓我注意到的是位元有以下這幾個檔位?3 1/2 位 = 3.50 Digits = 2000 counts

3 3/4 位 = 7.75 Digits = 4000 counts

3 5/6 位 = 3.84 Digits = 6000 counts

當時我就覺得很好奇查了一下[1]電錶DMM的解析度是用"counts",就類似ADC的bits,例如最常見的3 1/2位元 2000 counts,也就是最小會從1到2000,如果輸入檔位最大為2V,也就解析度為2/2000=0.001V,所以 3 3/4位元 4000 counts就是最大輸出為4000。

帳面看起來如果一樣的檔位如果買3 1/2位 2000 counts解析度為0.001V,那如果升級到3 3/4位 4000 counts不就可以變成0.0005V多了一倍? 但看起設計上為了符合10進位顯示,因為多不到10倍,所以只有最低的解析度並沒有變化,要買到解析度在高一階可能還是要直接買多一位而不是多這零點幾的等級。

ADC bits vs DMM counts

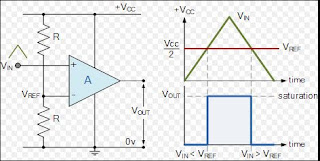

數位儀錶(DMM)跟早期的傳統指針儀錶不一樣,最後的顯示在螢幕的資訊都是數位訊號,所以都需要ADC (Analog to Digital Converter),一般來說都會說這個ADC是幾個bits 例如12bits, 13bits, 14bits ,ADC的總類很多[2],運作原理以簡單的SAR[3]為例子,拿上面2V的舉例說明。第一次先跟參考電壓2V/2 1V比較,如果比參考電壓高第一個位元1反之則為0,如果停在這裡就是一個1 bit的ADC或Counts =2,接著往下繼續比下去,以下面1.6V為例,第二次參考電壓Vref就等於上一個參考電壓Vref=1V+1V/2這一每比較一次就會多出一個bits,下面比了三次結果得到1.6V = 110,也就是3 bits 或counts = 8,所以比較12次 12 bits 就會等於4096 counts的解析度ADC。

|

| Wikipedia Comparator |

"Don't be fooled by ADC bits alone"

等校計算上可以參考[7] NI DMM Resolution這篇文章,但假設是Noise Free ADC那計算那10進位儀錶Digits與ADC Bits的關係就如下,要設計一個2000 counts的儀錶,那ADC的範圍就要大於兩倍也就是>2000x2(兩倍的原因是要包含+2000與-2000)。

所以至少要12bits 2^12=4096 ADC來設計,當然這裡是假設Noise Free的條件下。

Dual Slope ADC and Delta Sigma Type ADC

一般手持的文宣都會提到採用"雙積分A/D",積分型A/D架構上跟上面提到的flash/SAR的方式差異很大,理論上可以從Single Slope ADC展開,基本精神是用時間來換精準度,這其實跟RC低通濾波器一樣,如果你設計3dB頻寬是1Hz的Low Pass Filter,那你目標訊號就應該小於1Hz也就是你不可能在1秒鐘時間內取得有效的輸出訊號。透過OP Integrator調整電容的充放電時間或Clock速度就可以增加整個ADC的解析度如下圖所示,一樣的輸入電壓Vi 調整RC充放電會有不同的Resolution,但跟前面提到Flash ADC或SAR ADC相比,如果要12 bits的解析度,SAR只需要12 clock cycles,但積分型就需要4096 clcok cycles來完成。

Dual Slope ADC與Single Slope ADC很類似,YOUTUBE上面找了一些資源都幾乎是"印度腔",口音超級重聽的有點不清楚,以下是我聽了好幾個覺得講的最清楚而且也還聽得懂這位Dr. S. V. Viraktamath在說什麼的影片。

與Single Slope ADC最大的差異[8]是輸入訊號都經過積分器,OP Integrator [9]本身就是一個低通濾波器的響應,所以Dual Slope跟Single Slope ADC相較之下,如果Vi有個突然的突波訊號,會被積分器平均掉,再加上有Dual Slope ADC有固定的處理時間,所以對整個高頻的雜訊抑制可以壓抑的非常好。

Dual Slope ADC其實主要元件是一顆類比積分器來達成低雜訊的效果,另外一個常見到Sigma-Delta就比較像數化訊號處理的技巧[10][11]但本質上卻挺像的。

|

| From Wikipedia |

|

| 資料來源: 經濟部國際貿易局 |

Reference

[1] 如何從精準度,位數選擇萬用錶[2] ROHM Semiconductor 什麼是A/D轉換器?

[3] Maxim UNDERSTANDING SAR ADCS: THEIR ARCHITECTURE AND COMPARISON WITH OTHER ADCS

[4] Maxim UNDERSTANDING FLASH ADCS

[5] Wikipedia Comparator

[6] All about Circuit Flash ADC

[7] National Instrument DMM Resolution

[8] YOUTUBE Single Slope and Dual Slope ADC

[9] Op amp integrator

[10] MAXIM Sigma-Delta ADCs

[11] ADI Fundamental Principles Behind the Sigma-Delta ADC Topology: Part 1

[12] 半導體行業觀察 一文看懂ADC芯片,国产如何突围?

[13] 中国芯海:在中美贸易战和万物互联的混乱中寻求一片蓝海

沒有留言:

張貼留言